loading...

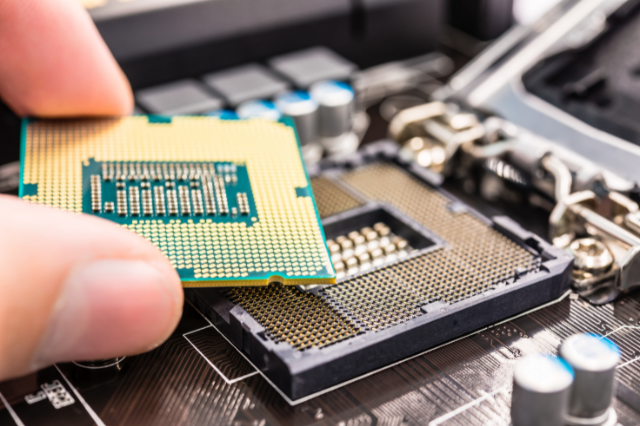

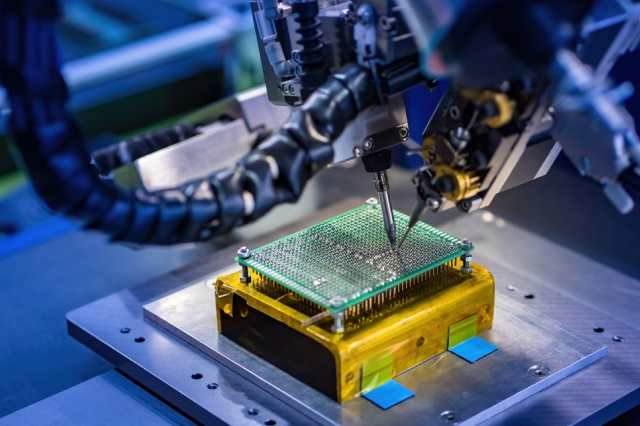

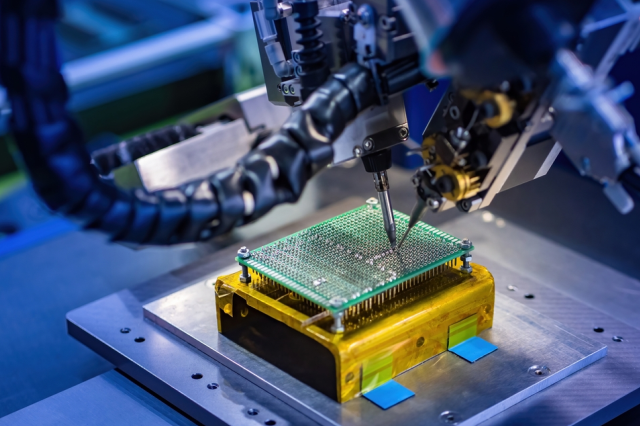

The year is 2026, and India's semiconductor sector is on fire. With the India Semiconductor Mission 2.0 accelerating, recent breakthroughs like 2nm chip tape-outs from Indian design teams, government ambitions for 3nm fabs by 2032 and 2nm by 2035, and estimates pointing toward nearly 1 million semiconductor-related jobs in the coming years, VLSI chip design stands out as one of the most promising and high-paying careers available today.

Demand is surging for expertise in AI accelerators, chiplets, heterogeneous integration, ultra-low-power designs for edge AI, EVs, IoT devices, and 5G/6G infrastructure. Companies are actively hiring skilled VLSI engineers—both freshers and experienced at global players like Qualcomm, Intel, NVIDIA, AMD, Samsung, Truechip and emerging Indian design hubs.

This practical beginner's roadmap will take you from foundational knowledge to job-ready VLSI chip designer status in 2026.

Step 1: Solidify Core Fundamentals (1–3 Months)

Strong basics are non-negotiable - weak foundations lead to repeated interview rejections.

Essential Topics:

2026 Insight: Low-power and variability-aware design is critical as nodes shrink further.

Resources to Use:

Target 80–90% mastery before advancing.

Step 2: Master HDLs Verilog & SystemVerilog (2–4 Months)

Most chip design begins at the RTL level.

Daily coding + simulation is key. In 2026, strong SystemVerilog + basic UVM knowledge opens doors to high-demand verification roles.

Step 3: Grasp the Complete ASIC Design Flow

Know the end-to-end process to position yourself better.

Key Stages:

Choose your focus early: Frontend (RTL + Verification – more fresher openings) or Backend (Physical Design/STA – rapidly growing in India).

Step 4: Select a Specialization & Gain Tool Proficiency (3–6 Months)

High-demand paths in 2026:

Essential Tools: Synopsys VCS/Verdi, Cadence Xcelium/Genus/Innovus. Add scripting (Python, Tcl, Perl) for automation edge.

Step 5: Build Hands-On Projects & Portfolio

Companies hire based on demonstrated skills. | Recommended Projects (4–6 minimum):

Use open-source PDKs for practice, but seek industry-tool access via training for real credibility. Join VLSI hackathons or share RTL on GitHub.

Step 6: Job Preparation & Final Push (1–2 Months)

Step 7: Choose Professional Training for the Winning Edge

While self-study covers theory, real progress comes from hands-on EDA tools, live projects, industry exposure, and placement support.

FutureWiz stands out as a leading VLSI training institute in India (headquartered in Noida, with strong national reach). We offer:

FutureWiz empowers thousands of engineers to break into the industry; many across India and beyond have landed roles after their structured training.

2026 is prime time to launch a VLSI career in India. The massive government push, global design migration, and exploding job creation make it one of the best fields for long-term growth and rewards.

Start now: Nail fundamentals, code daily in HDLs, build projects, gain tool exposure, and invest in quality training.

The chips driving tomorrow's AI, autonomous vehicles, and next-gen connectivity are being designed today. Position yourself to be the designer.

Happy learning, and best of luck on your VLSI journey!

How to Become a VLSI Chip Designer: A Beginner's Roadmap for 2026

How to Become a VLSI Chip Designer: A Beginner's Roadmap for 2026

A to Z on India, Japan & the Future of Semiconductor Industry: A New Chapter in Tech Collaboration

A to Z on India, Japan & the Future of Semiconductor Industry: A New Chapter in Tech Collaboration

RTL Design vs Physical Design: What's the Real Difference?

RTL Design vs Physical Design: What's the Real Difference?

The Future of the Semiconductor Industry: What Indian Students Should Know

The Future of the Semiconductor Industry: What Indian Students Should Know

Top 7 Career Paths After Completing a VLSI Course

Top 7 Career Paths After Completing a VLSI Course

Best Time Management Tips for Students Preparing for VLSI Careers

Best Time Management Tips for Students Preparing for VLSI Careers

Mastering VLSI Physical Design: A Comprehensive Course Overview

Mastering VLSI Physical Design: A Comprehensive Course Overview

The Complete FPGA and ASIC Guide

The Complete FPGA and ASIC Guide

Verilog Essentials: Mastering the Fundamentals of Hardware Description Language

Verilog Essentials: Mastering the Fundamentals of Hardware Description Language

Unleashing the Power of System Verilog: A Comprehensive Guide for Aspiring Designers

Unleashing the Power of System Verilog: A Comprehensive Guide for Aspiring Designers

Demystifying VLSI chip Design: Exploring the Core Concepts of VLSI Courses

Demystifying VLSI chip Design: Exploring the Core Concepts of VLSI Courses

Basics of VLSI - An Ultimate Guide

Basics of VLSI - An Ultimate Guide

Career Prospects After Completing A VLSI Course

Career Prospects After Completing A VLSI Course

Top 5 Reasons To Take Up A Professional VLSI Course

Top 5 Reasons To Take Up A Professional VLSI Course

Mastering VLSI Design: A Comprehensive Guide To Understanding Complex Integrated Circuits

Mastering VLSI Design: A Comprehensive Guide To Understanding Complex Integrated Circuits

Future-Proof Your Career With A VLSI Course: How Learning About Integrated Circuits Can Boost Your Job Prospects?

Future-Proof Your Career With A VLSI Course: How Learning About Integrated Circuits Can Boost Your Job Prospects?

System Verilog: An Overview

System Verilog: An Overview

Introduction to Hardware Description Language (HDL)

Introduction to Hardware Description Language (HDL)

Unlock The Potential Of VLSI Design With An Integrated VLSI Course Online

Unlock The Potential Of VLSI Design With An Integrated VLSI Course Online

Universal Verification Methodology:An Efficient Verification Approach

Universal Verification Methodology:An Efficient Verification Approach

How to Write a Verilog Module for Design and Testbench

How to Write a Verilog Module for Design and Testbench